Daily Image

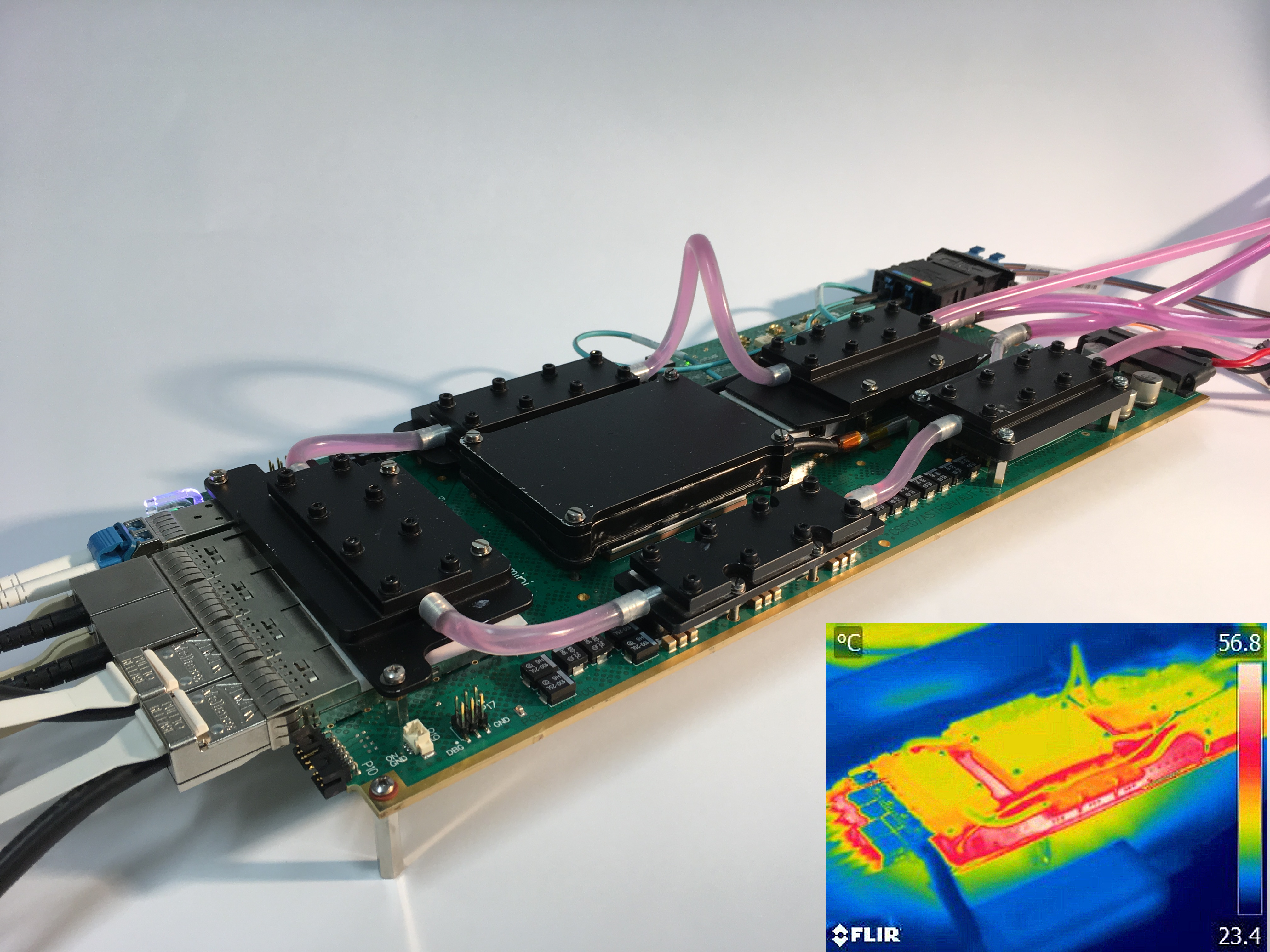

26-02-2018Heating up Gemini LRU

| Submitter: | Gijs Schoonderbeek / Leon Hiemstra / Sjouke Kuindersma |

| Description: | To test the power supplies and the cooling of Gemini LRU (Line Replaceable Unit) a heater firmware design has been made for the FPGA (Field Programmable Gate Array). In this design all transceivers are used, almost all combinatorial logic, look-up tables (LUT), flip-flops and internal memory. Intentionally, the low power multipliers are not used, to maximize power consumption. The design is toggling at a clock rate of 400MHz. The result is a FPGA power consumption of 142Watt. In the final application the power consumption of the FPGA is expected to be less due to a lower clock rate of parts of the logic and full usage of the low power multipliers. The heater design is used to verify that the power supplies have sufficient capacity. The core power supply for example has to deliver 158A. A voltage drop of 43mV is measured for this 0.72V power supply, which is slightly more than expected. The efficiency in the two stage power supplies is 73% on average. Therefore, an additional 47W of power from the power supplies has to be cooled. As shown in the image, only liquid cooling is used to cool the Gemini LRU. No fans are necessary for cooling. Even given the high power consumption, the maximum temperature of the FPGA was 74°C (recommended maximal temperature is 100°C). The temperatures measured in the power supplies at the bottom of the PCB (Printed Circuit Board) are all below 70°C. These devices are cooled through the board. These measurements show that we are on the right track for a fully liquid cooled SKA-Low correlator / beamformer. |

| Copyright: | DESP |

| Tweet |  |