Daily Image

28-05-2009Today's colloquium: An Automated Design-flow for FPGA-based Sequential Simulation, Pascal Wolkotte, U.Twente / Alcatel-Lucent

| Submitter: | Albert-Jan Boonstra |

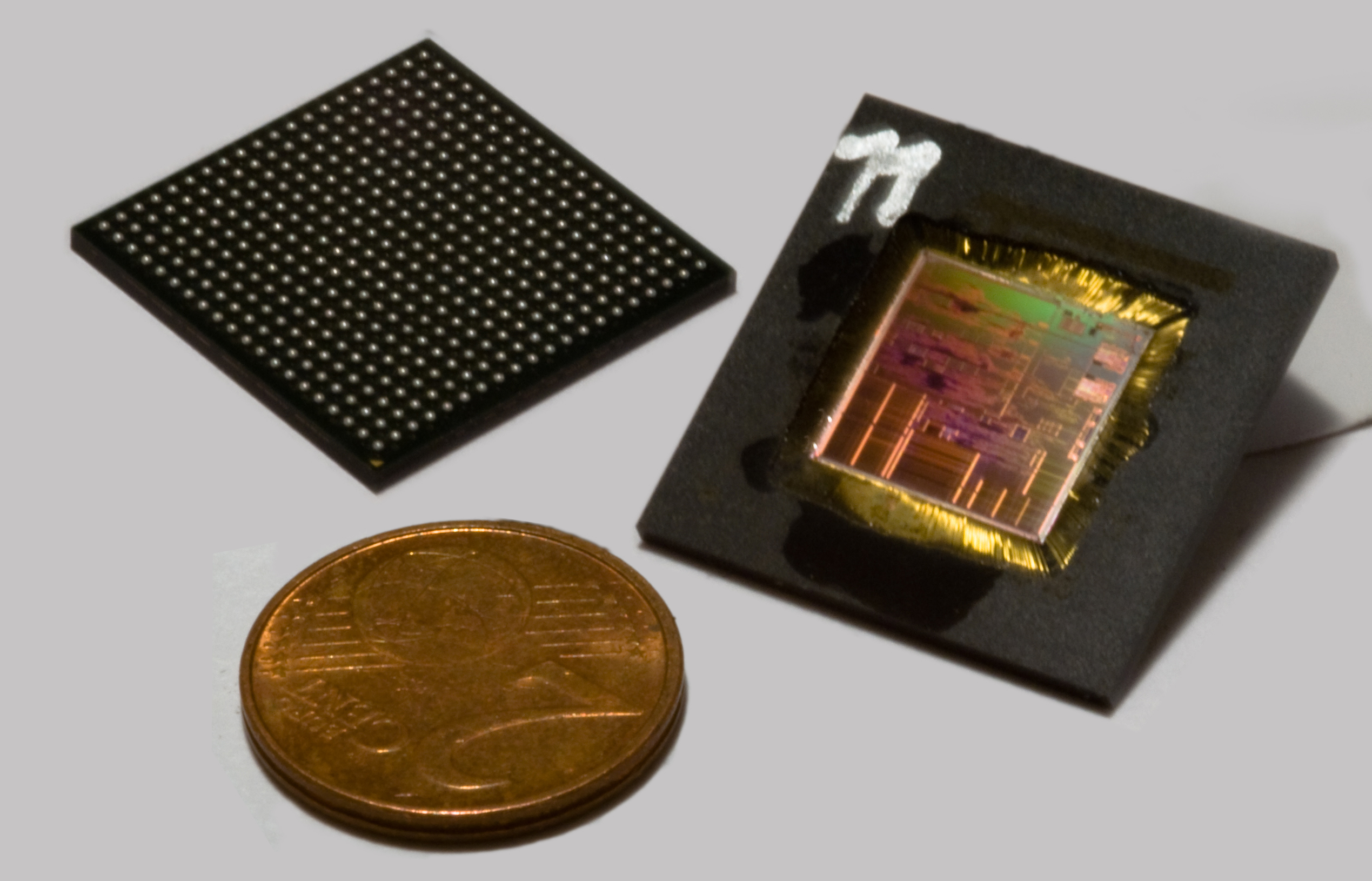

| Description: | During my PhD study I was involved in the European project "Smart Chips for Smart Surroundings (4S)". In this project we developed a energy efficient heterogeneous multi- processor IC, which is depicted above. One of the challenges during the design of this and future many-core processor architectures is the fast cycle-accurate simulations of these architectures before they are produced. In my talk I will present a novel technique in which we simulate the multi-core architecture in a programmable chip. Using the repetitive nature of multi-core architecture, i.e. identical components, we are able to make a good trade-off between hardware resources and the required simulation time. In comparison with a software based approach we are two to three other of magnitudes faster. Picture: The Annabelle Chip, developed within the 4S-project |

| Copyright: | Pascal Wolkotte |

| Tweet |  |